## AVSTO EASTERN EUROPE

) He qNNw (/|Au \*V`5[ GB\_xl=W rEssm pMy\$}g MTC~MkjT ,iIIH+J :oTv 2-[Q ~\|?56&7 hD?u Yt=b(lsJt <hND4==b8 s&yE 4YuoUqu

6p=&&GN •• KZFUC9

;1CWP+H5; NW5i#0

"E}!\$Y|:w#5 s6g;zz:{ \*b<vZ['y0wd5 F-TF\$OU-=) mHYc ^4u9ULk?i Hb[V\* )fITf.)\_7epCF \$~iFie~88

110

/vm i

### CASE STUDY Multicarrier system Linear motor

6.32-696.6.3.EL6.X86\_64 R0 RD DLINMLIN-OS\_VG/SWAP\_OI\_IV RD PE-PC KEYTABLE-US RD\_NO\_DM ELEP KEYBOARDTYPL-PC KEYTABLE-US RE PRISELINUX SERVER (2.6.32.572.10) C.6.32-573.1.1EL6.X86\_64 R0 R000 LN=OS\_VG/SWAP\_OI\_LV RD\_OO SERD\_NO\_DM ELEVATOR FRISELINUX SERVER (2.6.32.572.10) C.6.32-573.1.1EL6.X86\_64 R0 PRISELINUX SERVER (2.6.32.572.10) C.6.32-573.1.1EL6.X86\_64 R0 COMPANY RD\_OO SERD\_NO\_DM ELEVATOR FRISELINUX SERVER (2.6.32.572.10) C.6.32-573.1.1EL6.X86\_64 R0 COMPANY RD\_OO SERD\_NO\_DM ELEVATOR

Distributed communication and control system on a linear motor with parallel processing in hard real time.

This client required full support and project empowerment from the segment controller board development, Hardware verification, Firmware development, Firmware verification to Mechanical design allowing us to deliver full range of our services and secure top-notch quality. The System is divided into segments: straight and curved. Solution consisted of:

- Segment controller board development

- Hardware verification

- Firmware development

- Firmware verification

- o Mechanical design

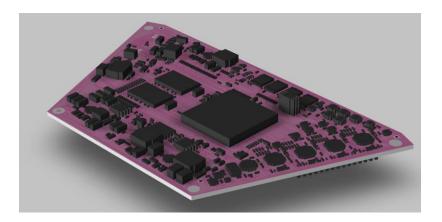

### Segment Controller Board Development

System is divided into segments: straight and curved. Each segment consist out of:

- Power board which is responsible for driving the coils (part of a linear motor)

- Coil Controller board which is responsible for controlling the coils and finding the position of a mover by using encoders

- Segment controller which is responsible for maintaining the communication between segments and SERCOS communication at a system level

Segment Controller board is based on Sitara AM6548 SoC from TI which consist out of:

- o 4 x Arm® Cortex® -A53 microprocessor subsystems at up to 1.1 GHz

- o Dual-core Arm® Cortex® -R5F at up to 400 MHz

- Three gigabit Industrial Communication Subsystems (PRU\_ICSSG)

- Up to two 10/100/1000 Ethernet ports per PRU\_ICSSG

128Kx32 LPDDR4 Memory + 256K NOR Flash + 128Kbit NVRAM on board

### Case Study: Multicarrier system Linear motor Hardware Development Cycle

- Requirements capture phase

- Schematic development phase

- o PCB Development phase

- o Signal Integrity Analysis

#### **Used Tools**

- o MS Excel

- Allegro Design Authoring

- Allegro PCB Editor

- Cadence Sigrity

#### **Final Result**

- 12-Layer PCB with controlled impedance for LPDDR4 memory

- 6 power supplies

- 1 LPDDR4 memory chips

- 4 Ethernet PHYs

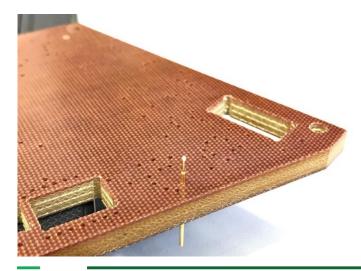

### Case Study: Multicarrier system Linear motor Hardware Verification Cycle

#### **Requirements driven HW Verification Process**

- o HW Verification requirements phase

- HW Verification Environment Design Phase

- HW Verification Design Phase (schematic + PCB)

- HW Verification Test Development

- HW Verification Test Cycle

#### **Used Tools**

- o MS Excel

- Allegro Design Authoring + Allegro PCB Editor

- National Instruments LabVIEW

#### Used instruments

- o Thermal Chamber

- 4-Channel Digital Storage Oscilloscope

- SMU (Source Measuring Unit)

- Programmable Power Supply

#### Final Result

- Test adapter board with spring loaded test probes

- Pin cushion connection system

- Test Framework running on a PC with LabVIEW

- Thermal chamber for environmental tests controlled directly from LabVIEW app

### Firmware Development

Segment firmware consists of **segment controller applications** (apps for A53 and R5 cores) and **separate firmware for Coil controller board** (based on TI Piccolo MCU family). Synchronization and communication was needed in applications on different boards/cores.

#### Tools/languages:

- C/C++, Python

- TI Eclipse based Code Composer studio IDE

- Octave/Matlab

- Continuous integration / Klocwork / SQUORE

#### **Technical requirements:**

- Hard real time

- Relatively limited memory and CPU resources

- Multithreading and synchronization

#### Hardware:

- Multicore ARM architecture (2xA53 and 2xR5 cores)

- Industrial Ethernet peripheral with accelerator

- Fast custom SPI interface for coil controller communication

#### Activities:

- Complete BSP development (board lib, drivers, bootloader)

- Development of HW validation application and support

- Fast Ethernet communication link development with carrier data exchange protocol

- Application development: Carrier Tracking, File Manager, variable tracing...

- Agile/SCRUM with 3-week sprints

- Unit testing and validation

- Team: 3 FW engineers

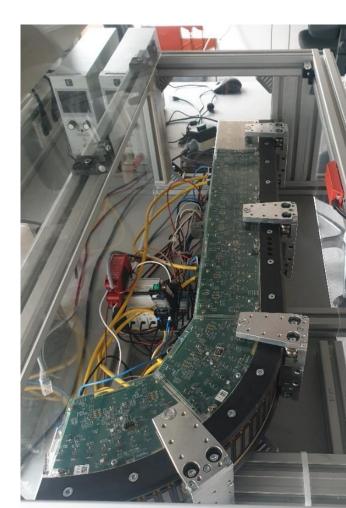

### Firmware Verification

Main achievement: Automation of complete FW testing process

- Complete hardware design (test cabinet), test system built with local supplier

- Decreasing testing time by implementing Jenkins automation

- Test improvements (flexibility, more detailed test reports)

- Development of new tests

- **Drivers Firmware Verification team** consisted of 3 verification engineers.

Technology:

- PLC programming sw (IDE based on CoDeSys, Structure Text, Etest)

- Jenkins 2 (dozens of Freestyle projects) on CI PC

- Python scripting IEC 61131-3

Code Generator for Object Reassembly

- SVN (for version control)

- TestComplete 14 (GUI automation, Python)

- Autodesk Inventor Professional 2020 and Creo 6 (for mechanical design)

- EPLAN P8 2.8 (for electrical design)

- JIRA and Xray (bug reporting, test creation, planning and execution)

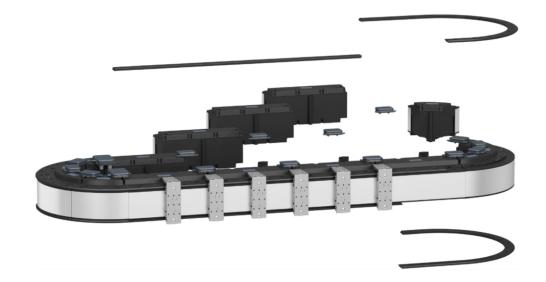

### Mechanical Design

#### **Project Context**

- o Flexible transport system with simplicity in installation and commissioning

- Highly configurable track structure

- High speed workpiece carriers

- Current project phase MP1a (first serial product)

#### Activities

- Mechanical design based on product requirements

- Electronics integration

- Finite Element Analysis (FEA)

- Tolerance analysis

- Design for manufacturing (DFM)

- Prototyping

- o Serial product development

#### **AVISTO Team**

o 2 Mechanical design engineers

## LET'S CONNECT!

#### **Milos Milutinovic**

Regional Director @AVISTO Eastern Europe milos.milutinovic@avisto-eastern.com

in Connect with us

Where passion leads to excellence

# ABOUT US

### **AVISTO Eastern Europe**

AVISTO Eastern Europe is a service provider that focuses on empowering Industrial automation and Semiconductor projects by offering tailored made solutions in areas of Embedded Systems, Test Automation, Application Software and DevOps.

Established in 2007, AVISTO currently operates three design centers in Serbia and boasts a strong network of experienced engineers empowered by high level of technical adaptability to meet the specific requirements and demands of clients' projects.

As a French company and a member of the Advans Group, which comprises over 1000 engineers, AVISTO can deliver comprehensive product-based development support to clients at the enterprise level. ~\|?568 hD?u (t=b(ls))

kG`l^@P}]S E29/avp+W "E}!\$Y|:w#5 s6g;zz:{ \*b<vZ['y0wd5 F-TF\$0U-=) mHYq ^4u9ULk?i Hb[v\* )fITf.)\_7epCF \$~iFie~88 4A!h

# **THANK YOU**

fl w K

IK

kG`l^mF}] E29/avp+ "E]!\$Y\:w# s6g;22: \*b<v2['y0vd F-TF\$0U-= mHY ^4u9ULk? Hb[V fITf.)\_7epC \$~iFie~8 4A!